Embedded Systems: ARM AXI3 vs AXI4 Bus Protocols1

Embedded Systems: ARM AXI3 vs AXI4 Bus Protocols

Introduction

ARM AMBA (Advanced Microcontroller Bus Architecture) is a bus interconnect that provides a way to connect different hardware blocks/modules (Masters, Slaves) within an SoC (System-On-Chip).

ARM has released different versions of the AMBA protocol, starting from the first AMBA revision restricted to the APB interface to AMBA5, which covers a wide variety of bus interfaces (AHB, APB, AXI) and enables hardware cache coherency between different managers in a single SoC.

AXI3 is a bus interface introduced in the AMBA3 protocol specification. It is a high-performance bus interface allowing high-bandwidth data transfer between hardware blocks within an SoC. Due to its performance, AXI3 is more suitable for high-frequency/performance SoC systems, especially MPUs like ARM Cortex-A processors.

AXI4 is an updated version of AXI3, part of the AMBA4 protocol specification. It introduces support for larger burst transactions, QoS (Quality of Service), and removes features like write interleaving and locking.

---

AXI Bus Interface

AXI provides a high-speed interface for high-bandwidth transfer rates, suitable for high-frequency SoC systems.

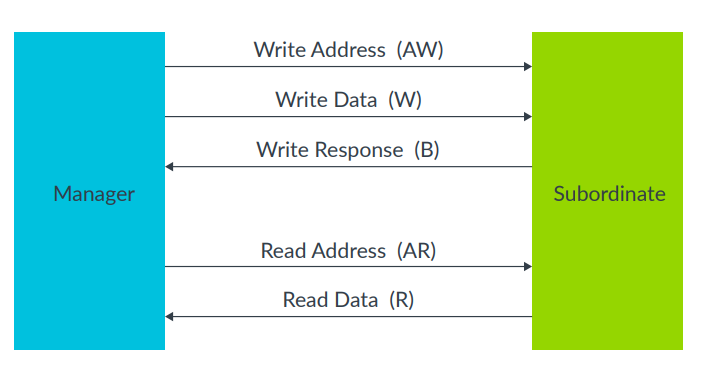

AXI bus consists of 5 separate channels (pipes):

- Write Address channel

- Write Data channel

- Write Response channel

- Read Address channel

- Read Data channel

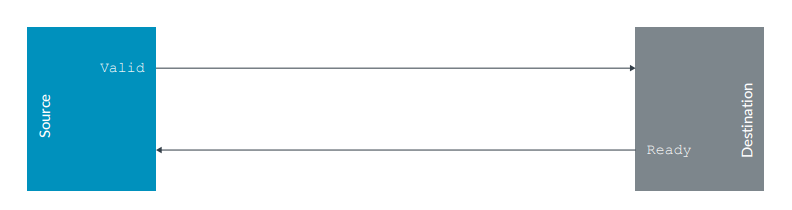

Each AXI pipe consists of a set of signals. While the signals differ by channel type, all AXI channels share a common handshake mechanism:

VALID: Set by the source (initiator) when data/command is ready to be sent.READY: Set by the destination (target) when ready to accept data/command.

AXI Channel Handshake Mechanism

This handshake mechanism is duplicated across all five AXI channels, enabling pipelined and asynchronous operations between source and destination components.

---

AXI Channel Signals

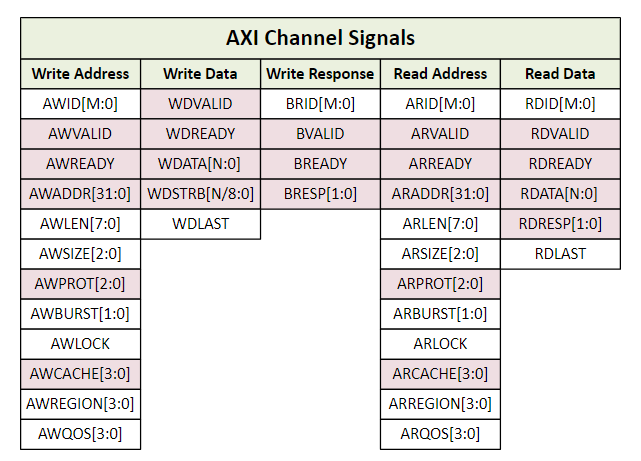

Below is a summary of different AXI4 channel signals:

---

AXI Key Features

- Pipelined transactions across separate channels.

- Full-duplex communication (read and write in parallel).

- Outstanding transactions: Masters can issue new transactions without waiting for previous ones to complete.

- Out-of-order completion: Later transactions may complete before earlier ones.

- Burst transactions: Transfer multiple data items using one address/control phase.

- AXI3: Up to 16 beats.

- AXI4: Up to 256 beats.

- Support for unaligned transfers.

---

AXI3 vs AXI4

| Feature | AXI3 | AXI4 |

|-------------------------------|----------------------------|-------------------------------|

| Burst Size | Up to 16 beats | Up to 256 beats |

| Write Interleaving | Supported | Not Supported |

| Lock Transactions | Supported | Not Supported |

| QoS Support | Not Supported | Supported |

| User-defined Signals | Not Supported | Supported (USER signals) |

Write Interleaving (AXI3)

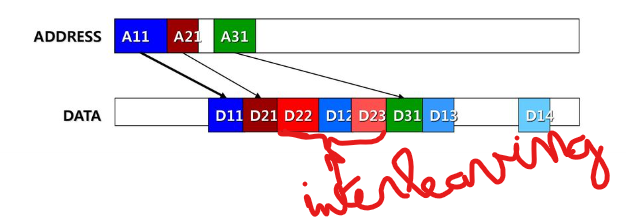

AXI3 supports write interleaving, which allows ongoing write transactions to be interleaved with others before completing previous ones. This increases flexibility but adds complexity to bus management.

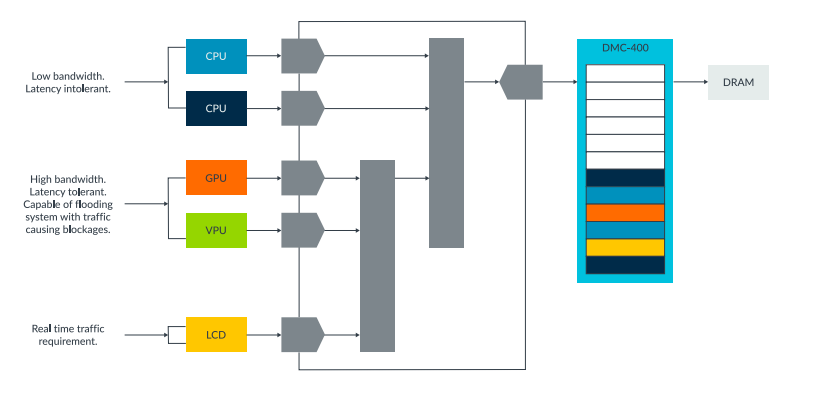

AXI4 QoS

AXI4 introduces Quality of Service (QoS) signals that prioritize transactions. For example, transactions from a CPU can be assigned higher priority compared to other masters.

---

Conclusion

Choosing AXI3 or AXI4 depends on system requirements. However, AXI4 is recommended due to its improvements and simplification over AXI3.

While this article highlights major differences, it's always best to consult the full ARM AMBA specification for integration details, especially when dealing with hardware/software debugging or SoC design challenges.

Embedded Systems: ARM AXI3 vs AXI4 Bus Protocols