The Power of Nothing: RISC-V’s Zero Register Explained

1. Introduction

In RISC-V, one of the most useful registers is the one that seems to do absolutely nothing. Meet x0, also called zero. It doesn’t store data, it doesn’t change, and no matter what you write into it, it stubbornly remains zero. At first glance, it feels pointless — why dedicate precious silicon to something that always returns the same value?

But this simple, hardwired zero register is far from useless. In fact, it’s a clever design choice that makes the RISC-V instruction set cleaner, smaller, and more efficient. What looks like “nothing” quickly becomes one of the most powerful tools in the architecture.

2. What is Zero Register?

The x0 register in RISC-V, also known by its ABI name zero, is a special-purpose register hardwired to the constant value 0. No matter how many times you try to write to it, the result is discarded. And whenever you read from it, you’ll always get zero.

This means x0 can’t store variables like other general-purpose registers (x1–x31). Instead, it acts as a built-in constant and a convenient placeholder. From the hardware side, it’s extremely simple — a register that doesn’t actually need to store anything, because the output is always zero.

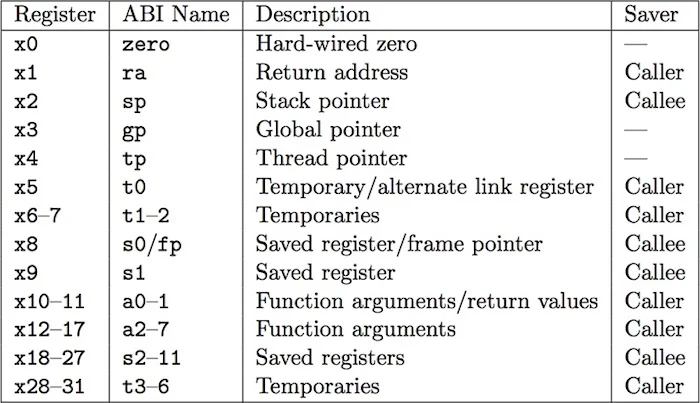

Figure 1: RISC-V General-Purpose Registers and Their ABI Roles

Credit: All About Circuits

The idea of a zero register isn’t unique to RISC-V. In fact, it comes from a long tradition of RISC designs. The MIPS architecture, which heavily influenced RISC-V, also included a special $zero register. The motivation was the same: simplify the instruction set by treating zero as just another register instead of needing dedicated opcodes. By carrying this idea forward, RISC-V not only inherits a proven design but also reinforces its philosophy of keeping the hardware as simple as possible while giving compilers powerful building blocks.

3. Why Does Zero Register Exist?

The decision to dedicate a register to “nothing” is not accidental — it’s a deliberate choice rooted in simplicity and efficiency.

Zero is one of the most common constants used in programming and hardware operations. Processors constantly compare values against zero, clear registers to zero, or branch when something equals zero. Without a dedicated zero register, every time the value 0 is needed, the processor must rely on special instructions, such as MOV r0, #0 in ARM.

RISC-V avoids these extra steps by building zero directly into the ISA. Because x0 is hardwired to zero, many operations become simpler and faster. For example, clearing a register doesn’t require a separate “clear” instruction — you can just add x0 to it.

This clever design choice also reduces the overall complexity of the instruction set, which is exactly in line with the philosophy of RISC (Reduced Instruction Set Computer).

4. Practical Uses of Zero Register

To make the role of the zero register concrete, we compiled the same small C function using online GCC compiler: arm-none-eabi-gcc for ARM and riscv-32bit-gcc for RISC-V. The function just checks whether its input is zero and returns 1 if true or 0 otherwise.

On ARM, the generated code explicitly compares the input against the constant zero:

is_zero(unsigned char):

mov r3, r0

cmp r3, #0

bne .L2

mov r3, #1

b .L3

.L2:

mov r3, #0

.L3:

mov r0, r3The instruction cmp r3, #0 literally encodes the constant 0 as part of the operation, and separate moves load either 1 or 0 into the register.

On RISC-V, the same function looks a little different:

is_zero(unsigned char):

mv a5,a0

bne a5,zero,.L2

li a5,1

j .L3

.L2:

li a5,0

.L3:

mv a0,a5Instead of embedding an immediate 0, the branch instruction directly uses the special zero register (zero). Likewise, when the result needs to be set to 0, the assembler simply refers back to zero instead of requiring a dedicated instruction to load a literal constant.

This highlights the advantage of having a dedicated zero register: the architecture doesn’t need special encodings for the constant zero, and compilers can always rely on a single, uniform mechanism.

5. Zero Register in Compiler Output

If you look at compiler-generated RISC-V code, you’ll quickly notice that zero shows up everywhere. Compilers love it because it saves them from generating special instructions whenever they need the constant 0. For example, when a variable is initialized to zero, the compiler can simply emit addi x5, zero, 0 instead of loading an immediate value, and branches like beq x10, zero, label are cheaper and more uniform than encoding a constant inside the instruction. This reliance on zero also keeps the instruction set lean: rather than bloating RISC-V with dedicated “clear” or “compare-to-zero” opcodes, the zero register becomes the one tool that unlocks them all — a great example of hardware and compiler design working hand in hand.

6. Conclusion

The RISC-V x0 register may look like nothing, but in reality it’s a clever design choice. By hardwiring zero into a register, the architecture eliminates extra instructions and keeps the ISA simpler and more elegant.