All Courses

Mastering RISCV Architecture Basics

Course Overview

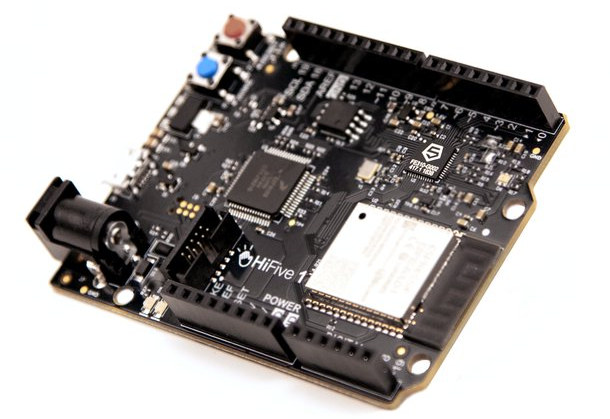

If you're eager to learn about the RISC-V processor architecture and write your first piece of code for a RISC-V-based product, you're in the right place. This course will introduce you to the key features and instruction set supported by the RISC-V architecture, as well as teach you how to debug code running on a RISC-V CPU.

---

What You Will Learn

Technical Details on RISC-V Main Hardware Blocks and Features:

- PMP (Physical Memory Protection)

- CSR (Control Status Register)

- Timers

- Interrupts/Exception Handling

- Different Faults types and how to Analyze

- Diverging Labs and Practical Tutorials

- Debugging RISC-V Based Code At C and Assembly Level

---

Course Bonus

As a Bonus in This Course, You Will Receive:

- Familiarization with RISC-V debugging techniques using Segger Ozone software

- Diverging labs and practical tutorials

- A set of easy-to-integrate drivers (e.g., PMP driver) for external code

- An initial C/Assembly/Makefile project to kickstart your learning

- Downloadable learning materials, including the initial C project

- 30 days of technical support available via email or contact form for any questions you may have